2017/07/31 芯片发展:持续缩小制程或是走向高阶封装?

高阶封装随着完整的流程及更优化的工具逐渐转为主流,本文提供市场意见左证。由于在单一芯片上集成异构组件的成本持续上升,高阶封装正迅速成为芯片制造商的主流选择。

虽然关于这项转变的传言已被讨论多时,但实际上转变的过程花了半个多世纪才得以实现。高阶封装从上个世纪60年代IBM的倒装芯片开始,而到了90年代,多芯片模块又得到了进一步提升,特别是在军事/航天用市场。尽管如此,因为硅面积特征尺寸微细化的成本较低,工具和专利配置的生态系统已经建构完成适于扩展,以及开始获利的时间也较明确等因素影响,它从未成为商业芯片制造商的首选。

随着finFET和双重曝光的推出,产业的经济结构在16 / 14nm处开始出现显著变化。预计每个新节点制程之后,设计和制造成本将会上升。收缩特征将需要5nm的新材料用于触点和可能的互连,以及在5nm或3nm(最可能的是全栅FET)的新晶体管结构。然后还有高数值孔径的EUV,以及新的蚀刻,沉积和检测设备。总而言之,这些步骤增加了在高级流程中开发和制造芯片的成本,因为芯片的市场机会较少,足以抵消成本。

这些因素对于半导体行业来说并不意外,尽管EUV的持续延迟迫使设计团队采用多层次的金属层和金属层。然而,需要时间来开发可行的替代方案,并证明和改进它们。 EDA供货商现在正在提供工具和完整的流程,使用各种封装选项构建芯片,并且在高可见性市场中有足够的高级封装芯片生产,以证明该选项可以从供货商,如苹果,AMD,华为,思科,IBM和赛灵思,以及3D NAND,高带宽内存(HBM)和混合内存立方体。

另外,最大的IDM中的英特尔和三星两家厂商,现在提供低成本专有桥接技术的代工服务。除了2.5D和3D选项之外,所有主要的封测代工厂OSAT都提供一个或多个版本的扇出芯片级封装。此点也反映在高阶封装各市场区隔皆有增长的趋势上。

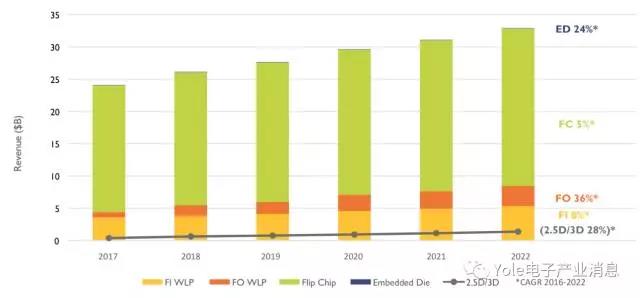

图。 1:平台别高阶封装收益,以数十亿美元计。

自动化工具设计

这个市场成长的迹象之一就是自动化工具。在三大电子设计自动化EDA供货商中,Cadence是第一家提供封装工具的公司。该公司在二十世纪的九十年代就跃升至市场,并且基于模拟技术并未走向组件尺寸缩小的观察,自从千禧年开始至今,持续投入研究开发工具。然而,如此愿景却花了近15年的时间才逐渐跃升主流,并让其他的EDA供货商开始视其为值得研发投资的机会。

本月早些时候,西门子旗下的Mentor也推出了先进封装的流程和新工具。“这个过程现在类似于硅流程。” 该公司高阶IC封装解决方案板系统部门的产品营销经理Keith Felton说。 “我们认为将出现多组设计套件。因此,您将看到两组用于扇出芯片级封装的套件,个别都有些微差异,并排并排,堆栈裸片,基板上的芯片(CoWoS),高引脚数覆晶芯片和系统级封装SiP“。Felton表示,这将与其他包括可制造性设计DFM工具以及PCB分析和验证等的工具一起使用。

“这完全就是以物理为基础的应用。“ANSYS总经理兼副总裁John Lee表示,”这不仅仅是关于半导体。它是热分析和机械模拟。如果您从台积电的整合型扇型封装InFO来看,您将拥有晶圆级封装的硅片。因为有明显的物理效应,您需要进行同步热应力分析模拟。这可能包括7nm,10nm,16nm或甚至更传统的制程技术。但散热片影响系统的可靠性。所以,如果你研究电子迁移效应,但不讨论热电,那么你可能对世界有悲观的看法。如果你不觉得悲观,那可能反而是更危险的。“

Synopsys公司董事长兼联合首席执行長Aart de Geus表示,真正的关键是能够将整个系统可视化,并构建能适用于各种封装方案的组件和工具。“因此在发展IP时,您必须确保它的属性于各种情况下皆适用。总体仿真是系统仿真,而各种形式的复数芯片组成该系统。这也包括软件。将人们建立的产品模型化和产出原型的能力至关重要。包括数位和数位/混合信号。"他同时指出,这也还包括硬件仿真和建立软件样品原型。 de Geus表示:“您需要能够在您还没有的硬件上运行软件”,无论是在一个封装package还是在7nm SoC上。"

但添加这些高阶封装的工具将大大有助于为这些方法增加可预测性。

“EDA工具将带来重大的改变。“TechSearch International公司总裁Jan Vardaman表示。“没有设计工具,你能做的事情有限,接下来,我们将 会看到更多设计工具的使用。在任何情况下,如果你能够正确地进行组件分区,你会想要依照设计中较传统的制程进行。为此,设计工具是非常需要的。”

封装策略

“随着产品一代代的发展,我们第一代的方法就成为常态基准。”ASE日月光产品资深总监Ou Li表示。 “随着发展更先进产品的过程,我们可以把我们所学到的经验应用于其他的产品。希望通过学习曲线和机器学习和处理能力,我们可以有余力容纳其他的产品。所以最先进的产品会受到需求量和市场规模的支持。对于更小、更分散的市场,可能就不是那么一回事。但是因为我们已经从其他产品的经验学习,对于产品规格的需求,导入的过程可能会变得容易些。“

然而,市场零碎分散化仍然有其影响。随着设计越来越多地通过软件来定义,而不是通过使用通用硬件平台实现将软件编码到软件中 - 没有两个设计是相同的,而终端客户的要求更加严格。

“每个不同类别的产品都有不同的挑战,”Li说。 “但是对于系统包装,我们必须满足严格的客户要求。这是各种高阶封装技术的共通趋势。“

下一步是开始构建平台,以便更快速地置入送出芯片,并使用封装技术进行所谓的“大规模客制”。

STATS ChipPAC全球产品营销副总裁Scott Sikorski说:“真正的机会是存在于能够将所有内容整合到一个平台中。此举将会带动下一阶段的成长。 eWLB(嵌入式晶圆级球栅数组)是以不同方式构建既存产品的绝佳机会。“

企业开始采用此方式的速度还有待观察。过去18个月来,市场对扇型封装的需求一直很高,但开发这类装置的能力却很有限。但最近半导体外包构装测试服务厂商(OSATs)产能的提升已改变了这样的状况。

Sikorski表示:“现在有开发更多装置的产能增加,而且您将会在近期内看到更多的装置。”他并指出,运用封装作为一个整合平台的手法也开始受到关注。“这是一个非常低成本的方法,因为你已经拥有所有的建构基础。我们原来以为这将是一个PoP格式,在芯片周围有通孔结构(through-viastructure)。但是在我们提出建议的当下,供应链还没有准备好。“

学习曲线

过去几年技术的一大跃进源自于在多样化的市场使用高阶封装的经验。 eSilicon营销副总裁Mike Gianfagna说:“从事封装、测试和DFT可测试设计的人们现在是摇滚巨星。 “然而封装的复杂性也在增长。使用2.5D技术,您必须考虑硅基板、热能和机械应力以及更多的分析。因此,封装和DFT团队在开发过程中的较早阶段开始参与。 DFT部分可以影响整个进度时程。“

目标是在设计过程中增加更多的可预测性,这需要时间整理。然而,高阶主管和分析师都认为可预测性正在改善。

“这还没成为固定流程,因为任何新技术或技术节点制程都有学习曲线,”Gianfagna说。

Cadence的工程团队总监Brandon Wang说,现在所有主要的网通公司都在采用2.5D设计。“明年市场上将可以看到新产品,”Wang说。“同时你也将看到更多的传感器被用在在其他芯片封装中,特别是MEMS芯片。尽管如此,这些设计的本质是截然不同的。直到最近,许多设计都是锁定个别特定的市场区隔,因此很难为它们创造出一套共通的方法。但由于传感器价格低廉的影响,因此大致的发展方向是它们将成为更标准化的单位零件。这比较像是一种从平台面着手的方法,一个能让您快速达成所需成果的方式。”

为了实现这一点,需要一个传感器参数与其余电子组件同时进行调整的多晶粒共同设计。

“我们将会在各处配置传感器,而您会需要与我们一起优化这些传感器。” Wang提到。“它将变得更加以电为中心。电子设计工程师仍然专注于终端设备的产量,平台将使他们能够专注于电气性能并与传感器平台交流沟通。每个系统都会配置传感器,但您可以设计一个针对特定用途进行优化的传感器集线器。如此一来,如果你有五个传感器,它的价格将不是五倍;也许只有1.3倍。而且由于它是一个标准的传感器或传感器集线器,所以你清楚知道它将如何运行。”

对于平台的着重未来会是这一战略的关键。这使得将设计中增加异质性变得更加容易,同时到也带来更可预测的结果。此外,平台也可以大大降低设计成本,因为它们具有规模经济性和让更多企业参与竞争的能力。

ARM的市场开发资深总监Bill Neifert说:“客户寻求我们的指导和设计建议的情况越来越多。 “去年我们提出了设计指南,但并不只是与处理器相关。同时也和性能和功率数字有所牵连。我们还有一个预先构建的软件平台来帮助他们克服传统方式所会遇到的障碍。“

其中的一个问题是,唯一解决特定问题的最佳方式已不存在。

在过去,进度是由流程节点制成衡量的,对异质性的强调大幅增加了选择的种类。并非所有内容都必须集成到单个裸片中,并且在许多情况下,即使在同一个进程节点,IP也会从一个代工厂到下一个显著变化。

“我们现在正在与我们的主要合作伙伴一同投入设计的各个方面。” Neifert说。“甚至包括早期的寄存器传输的设计RTL,虽然这在IP级别以外更常在子系统级别完成。并且当前的设计也纳入各项从安全需求(safety requirements)到安全可靠性(security)的考虑。我们试图找出任何不够完美的环节,所以当我们把所有部分整合在一起时,不至于出现潜在的问题。”

而这仅仅是个开始。 EDA工具和流程的推出将把对这些装置设备的控制提升至另一个层次。

Mentor的Felton说:“您将看到更高的精准度、更小的功能尺寸,我们将能够开始用3D影像方式评估设计。您将能够为基板的”what if假设“情境制定蓝图,也将能够拥有包含热验证的芯片级产品。”

努力的目标是对不同的封装选择进行更前期的分析,这对于选择基板、封装类型,IP以及芯片之间和芯片之间的互连将变得特别重要。

“这牵涉到不同类型的使用者,”Felton指出。 “有IC半导体设计工程师,他们正在提出可能是芯片堆栈stack die或层迭PoP封装的封装方式,然后交给另一个团队进行封装设计。这需要专门的解决方案和流程。它正在将其从机械转移到EDA。“

结论

在摩尔定律被提出的52年后,单一芯片的芯片设计和制造已可被精准掌握。整个生态系统都已经到位,像一个经过精准调校的机器一样平顺运作。高阶封装技术则还需要时间才能实现相同程度的稳定性,但是现在系统原有的障碍因素已被充分解决,也有足够的封装成功案例,投身此领域已经不再是一场豪赌。随着更多的工具和可预测性的提升,扇出型和2.5D封装导入的成本也会持续下降。

大多数行业内部人士认为,少数几家公司将继续缩小最先进节点制程上的逻辑单元,但越来越多的公司将会围绕这一逻辑在单一封装增加更多元素。未来的走向是异构的,而混合这些元素的最简单的方法将是透过封装,而不是一个单一的晶圆。